最近看到一个关于上下拉电阻的问题,发现不少人认为上下拉电阻能够增强驱动能力。

随后跟几个朋友讨论了一下,大家一致认为不存在上下拉电阻增强驱动能力这回事,因为除了OC输出这类特殊结构外,上下拉电阻就是负载,只会减弱驱动力。

但很多经验肯定不是空穴来风,秉承工程师的钻研精神,我就试着找找这种说法的来源,问题本身很简单,思考的过程比较有趣~

二极管逻辑

今天已经很难看到二极管逻辑电路了,其实用性也不算高,不过因为电路简单,非常适合用来理解基本概念。

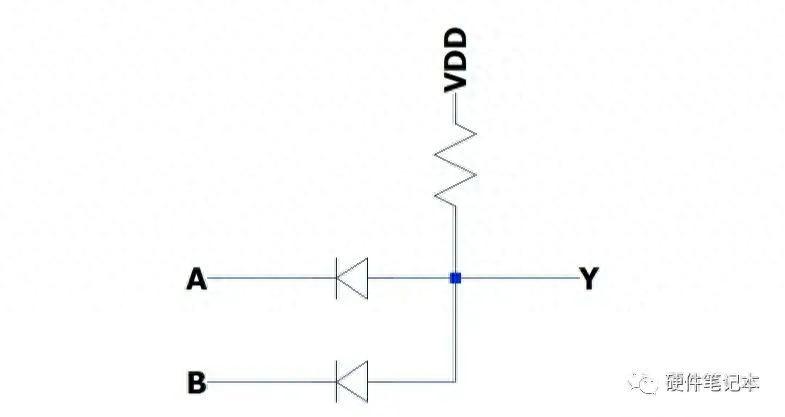

一个最简单的二极管与门如下图所示。与门实现逻辑与操作Y=A&B,即A或者B任意为L的时候,输出Y为L,只有当A和B都为H时,Y才为H。

基本二极管与门

假设二极管无导通压降,在这个电路中,二极管充当了单向开关的角色,当A和B等于VDD时,两根二极管反向截至,Y被电阻上拉到VDD,这是Y就是H;当A或者B任意一端为GND时,二极管导通,因为二极管导通时电阻很小,远小于上拉电阻,所以Y被拉到了GND,即逻辑L。

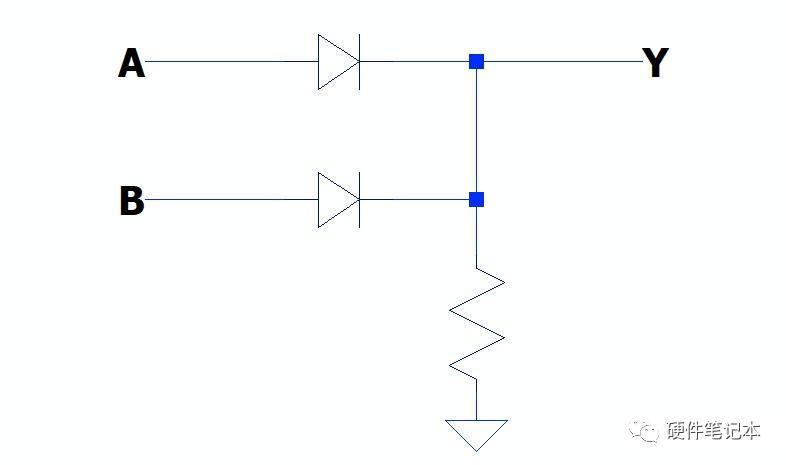

至于二极管或门,只要把二极管转一下,再把电阻从拉到VDD改成拉到GND就可以了,非常简单。

基本二极管或门

基本原理

你看,在这么原始的逻辑电路中就已经出现了上下拉电阻,这里面的原理也非常简单粗暴:利用开关的闭合(电阻为0)和开启(电阻无穷大)的特性,配合电阻,就可以轻松实现两种电压的输出。

这种电路还有一个变形,就是用恒流源取代电阻,一方面集成电路工艺,恒流源比电阻更容易获得,另一方面恒流源的驱动能力也更好。

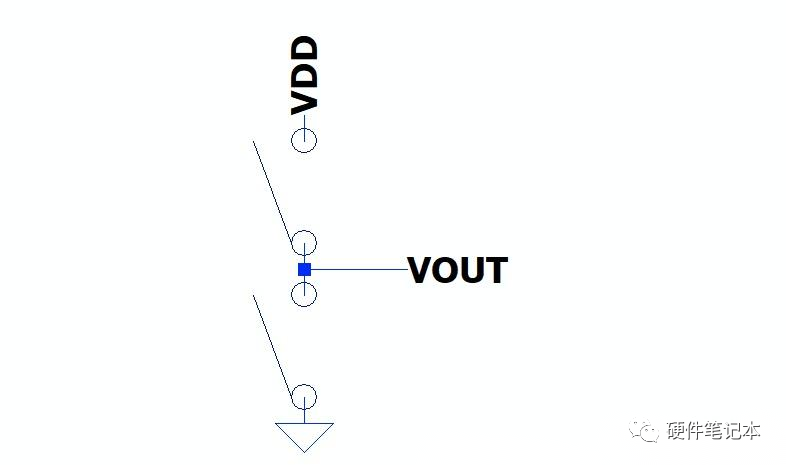

根据开关和电阻(或恒流源)的相对位置,有以下基本电路:即开关接到GND(L)或开关接到VDD(H)。

这几种电路都是由开关的闭合或开启决定了VOUT是VDD还是GND。

开关的相对位置不同,还决定了电路在某一状态下的驱动能力:开关的导通电阻为0,可视为驱动力无穷大,可是电阻(或恒流源)的驱动能力呢,只有VDD/R(或者恒流I),这就导致了电路在输出H或L的时候驱动能力不对称(换一个说法,就是电路在输出H或者L的时候,输出阻抗不一样)。

除了驱动能力的问题,这种单开关加电阻的模式还会带来静态功耗的问题,因为只要开关闭合,不管外部有没有负载,都会消耗电流。

既然开关的驱动力比电阻强,那么能不能把电阻也换成开关?恭喜你,发现了现代CMOS逻辑电路的基本单元:俩互补的开关。这样不管输出H还是输出L,驱动能力都是无穷大!好的,这时候上下拉电阻就不见了。

这样两个开关的电路还多出来了一种状态:当两个开关都开启时,VOUT即不是VDD也不是GND,而是一个悬空的状态(即高阻态,Hi-Z),这时候外部给什么信号它就是什么状态。这样又出现了一个新的逻辑门大类:三态逻辑门。